Ready

Outline of presentation

- Why using the ANSI C

- What is HCE

- How HCE works

- Example of HCE use

- The DRC co-processing boards

- HCE performances

- Conclusions

# Outline of presentation

#### Why using the ANSI C

- What is HCE

- How HCE works

- Example of HCE use

- The DRC co-processing boards

- HCE performances

- Conclusions

# Why an ANSI-C compiler for FPGA?

- Don't need HW-engineering knowledge

- Don't request specific expression of parallelism

- Don't need to learn a new language/dialect

- May use any C compiling environment to test and debug the application

- May port your codes under any new computing technology supporting ANSI-C (for sure a proprietary language will not be supported)

### Is ANSI-C adequate to express algorithms?

- ANSI-C can represent any untimed algorithm and is widespread used to express scientific algorithms.

- To efficiently support not standard data types it can be useful to extend the ANSI-C with data types defined by the SystemC standard: HCE supports the sc\_fixed and the sc\_bv data types.

# Outline of presentation

#### Why using the ANSI C

- What is HCE

- How HCE works

- Example of HCE use

- The DRC co-processing boards

- HCE performances

- Conclusions

### What is HCE

- The HARWEST Compiling Environment (HCE) is a C to VHDL optimizing and parallelizing compiler

- It is the first outcome of the HARWEST research project, funded by the Italian Ministry for University and Research, aimed at creating a fully automated HW/SW co-design environment.

### What is HCE

- The HARWEST Compiling Environment (HCE) is a C to VHDL optimizing and parallelizing compiler

- It is the first outcome of the HARWEST research project, funded by the Italian Ministry for University and Research, aimed at creating a fully automated HW/SW co-design environment.

- Let us see the HCE Design Flow

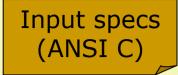

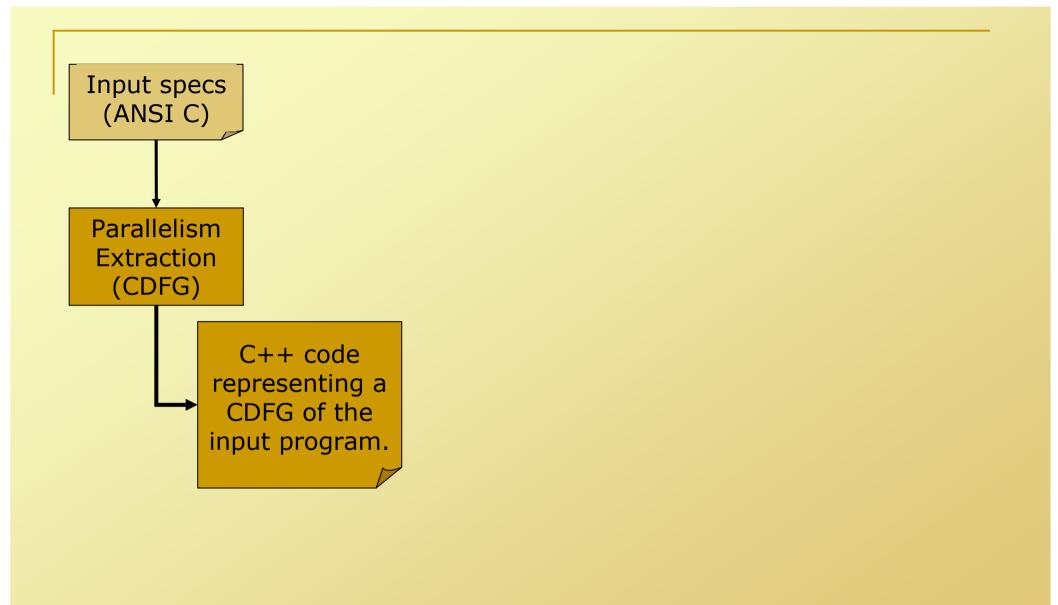

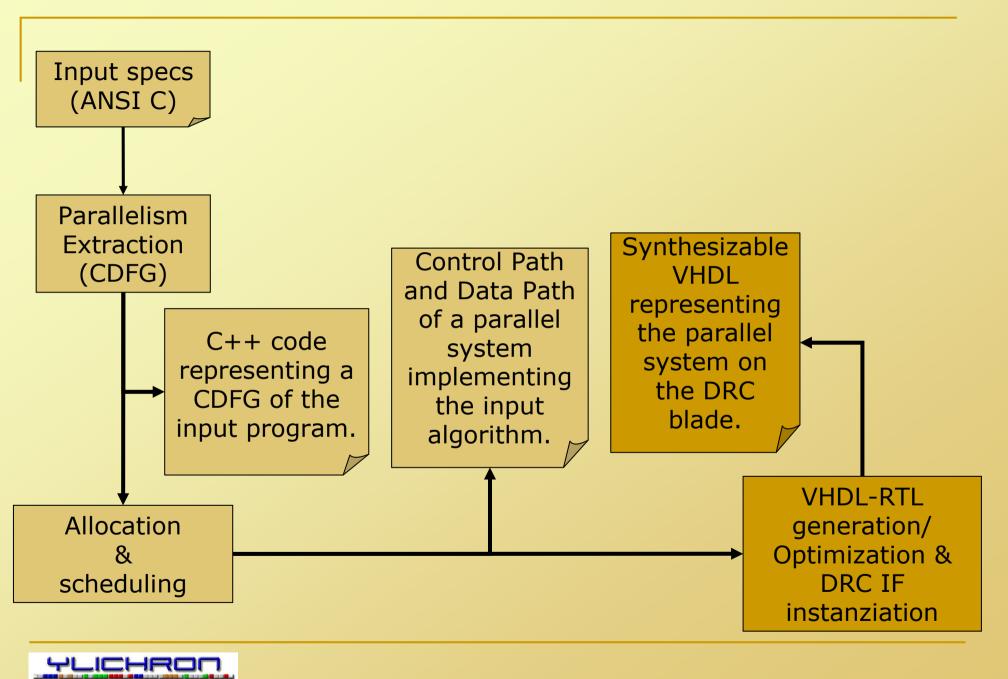

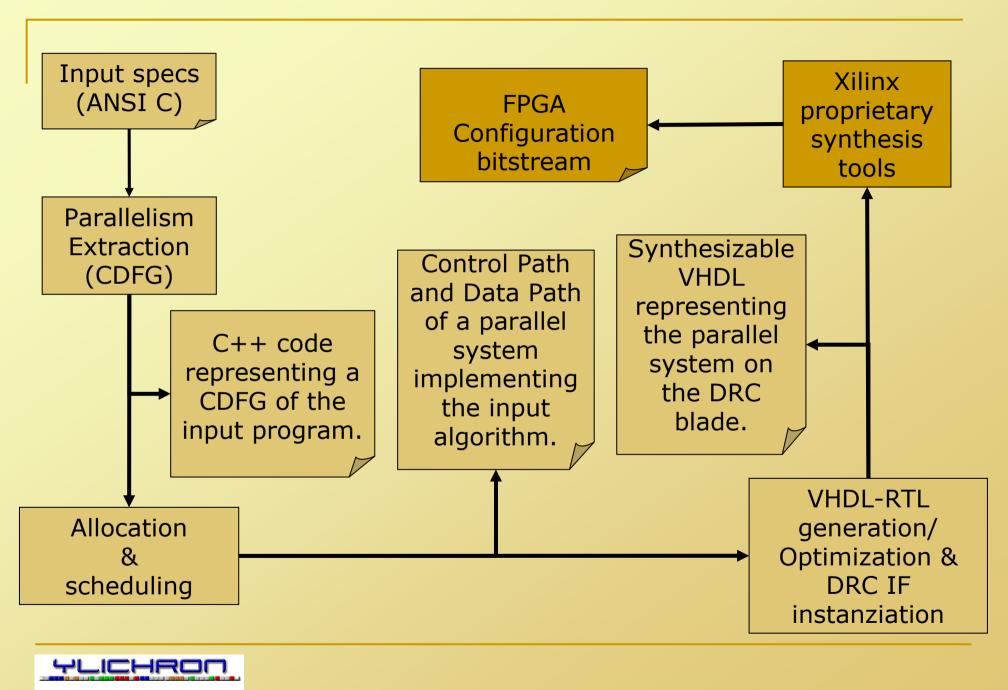

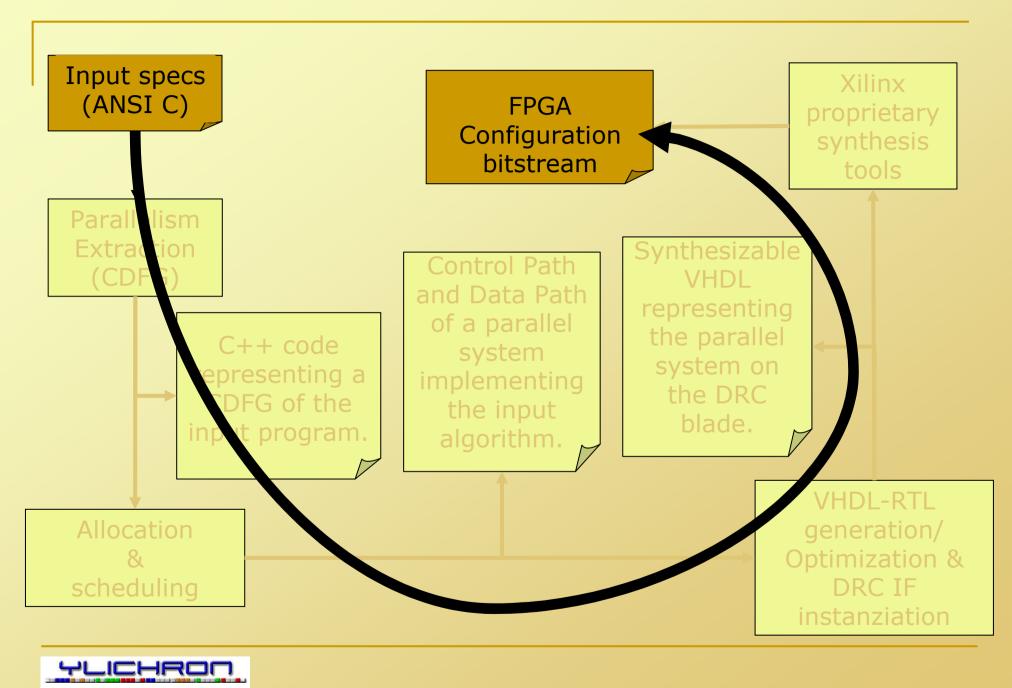

### How does HCE work?

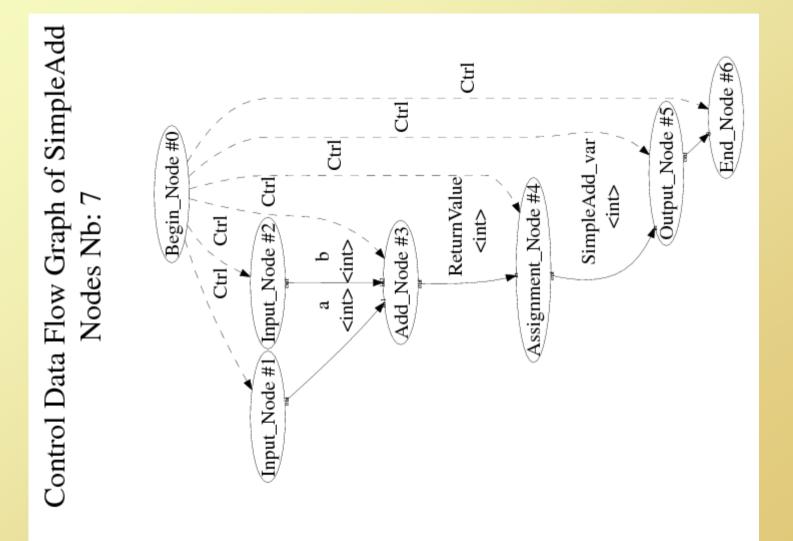

- The C code is translated into a parallel representation, i.e. the Control Data Flow Graph model (CDFG): roughly each operator corresponds to a CDFG node;

- At the CDFG level some basics optimization, aimed at reducing the complexity of the graph, are performed: constant folding/propagation, common sub-expression elimination, invariant code motion, dead code elimination

### How does HCE work?

- Within the HCE we created a library of computing modules which are the building blocks used to set-up the final parallel architecture.

- The modules can be combinational, pipelined, multicycle, asynchronous.

- The CDFG is allocated and scheduled onto the available HW modules, which nearly map 1-1 with the nodes: every node has at least one module which implements it;

### Which HW modules does HCE contain?

- modules in the library:

- Pipelined (\*, +) and multi-cycle (/) floating point operators

- All the family of operators for char, int, fixed point

- The basic math functions (sinf, cosf, tanf, sqrtf, logf, expf)

- The rand() function

- Modules to manage pipelined memory banks with any (<= 64) address and (2<sup>k</sup>) word length

- The library can be extended with user defined modules

### How does HCE work?

The set of modules to support the C program can both manually and automatically be fixed.

In the manual case it is possible to specify, for each C function, the multiplicity of the modules that will be used to implement that function: in such a way the user may control at which level of granularity the parallelism is exploited

### How does HCE work?

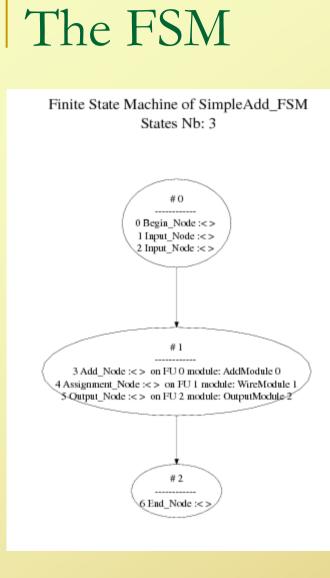

- An efficient scheduling algorithm creates a Finite State Machine which executes, in the (~) shortest time, the original algorithm onto the available resources

- Optimized VHDL is generated by analyzing FSM

- Once the original C program has been translated into a synthesizable parallel architecture, the proper interface with the DRC environment is added

## May algorithm hierarchy be exploited?

- Each C function may use another function void f1(param\_list\_1) {...} void f2(param\_list\_2) {...; f1(actual\_param\_list); ...} void main\_f(param\_list\_main\_f) {...,f1();...;f2(); ...}

- Each function, starting from the innermost (i.e. f1), is synthesized and constitutes a new (asynchronous) module (m\_f1) on which the node f1() can be allocated whenever invoked (both in f2() and in main\_f().

void **BlockMatrixMAC**(float BA[N][BS],float BB[N][BS],float BC[N][BS],int step)

```

int i,j,k, base_k, BlockNumber;

for (BlockNumber = 0; BlockNumber < NbProc; BlockNumber++){</pre>

base k = ((BlockNumber+step)*BS)%N;

for (i=BlockNumber*BS;i<(BlockNumber+1)*BS;i++){</pre>

for (j=0; j<BS; j++)

for (k=0;k<BS;k++)

Implemented with

BC[i][j] += BA[i][k] * BB[base k + k][j];

1 FP Add

1 FP Mul

void rotateMatrixBA(float BA[NbProc][N][BS] /*#HWST split 1 NbProc */)

{ }

void CannonMM(float BA[NbProc][N][BS] /*#HWST split 1 NbProc */,

float BB[NbProc][N][BS] /*#HWST split 1 NbProc */,

float BC[NbProc][N][BS] /*#HWST split 1 NbProc */)

for (int step = 0; step < NbProc; step++){</pre>

int i;

/*#HWST split */

for (i=0; i<NbProc; i++)</pre>

Implemented with

BlockMatrixMAC(BA[i], BB[i], BC[i], step);

NbProc

rotateMatrixBA(BA);

BlockMatrixMAC

```

# Outline of presentation

- Why using the ANSI C

- What is HCE

- How HCE works

- Example of HCE use

- The DRC co-processing boards

- HCE performances

- Conclusions

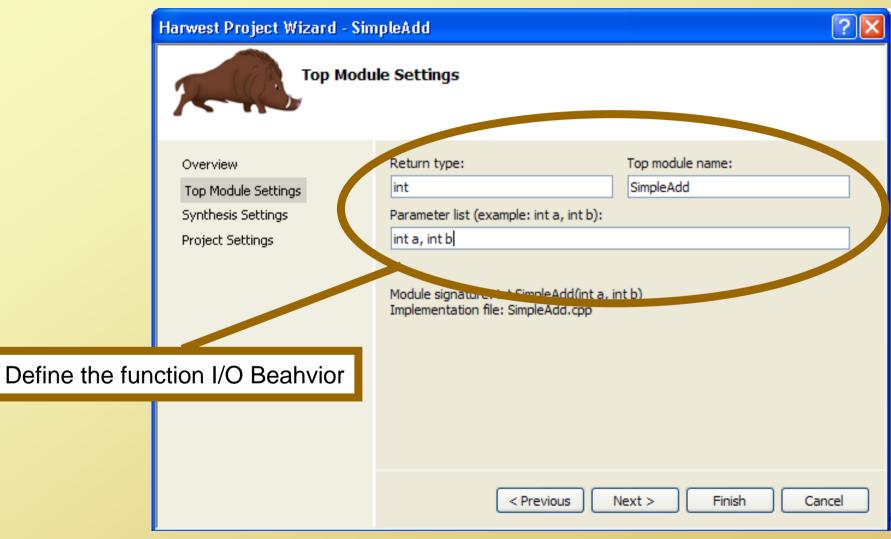

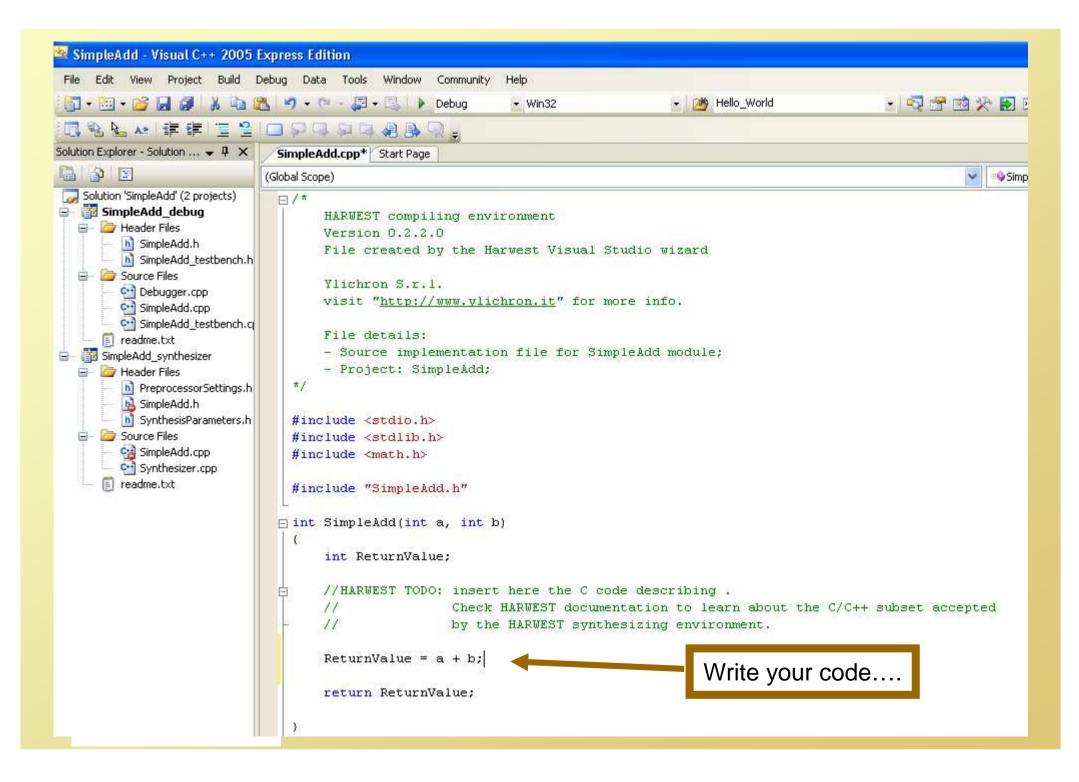

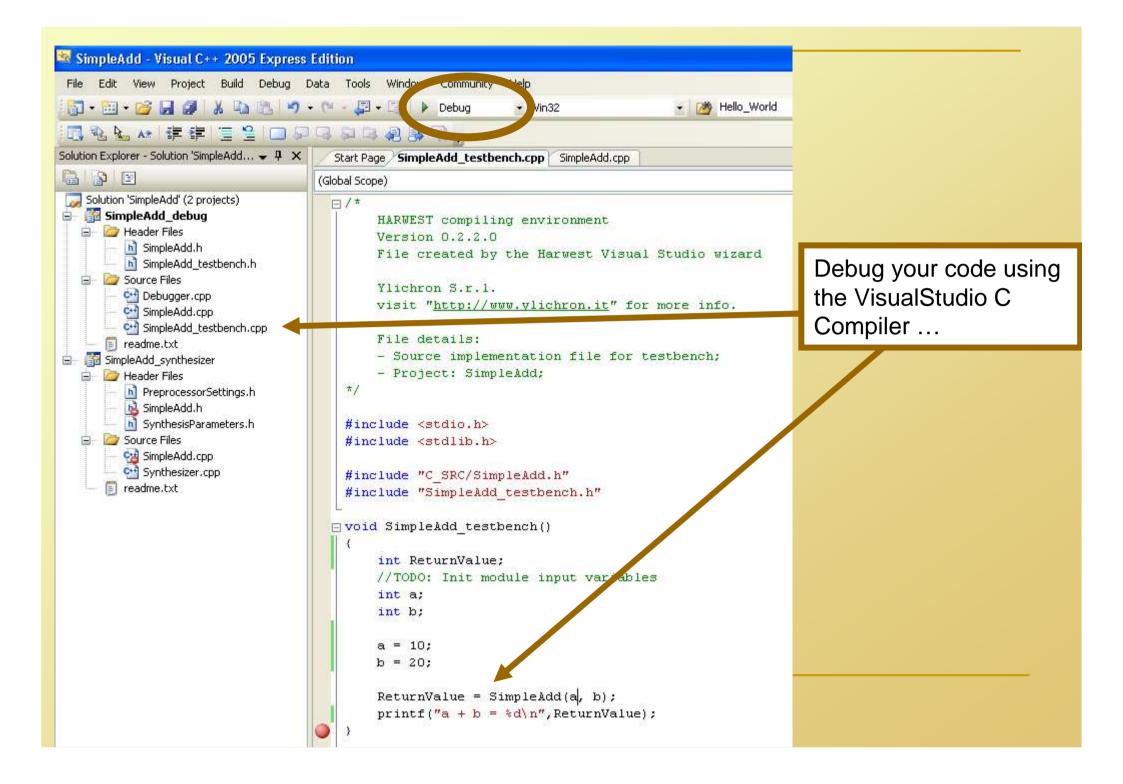

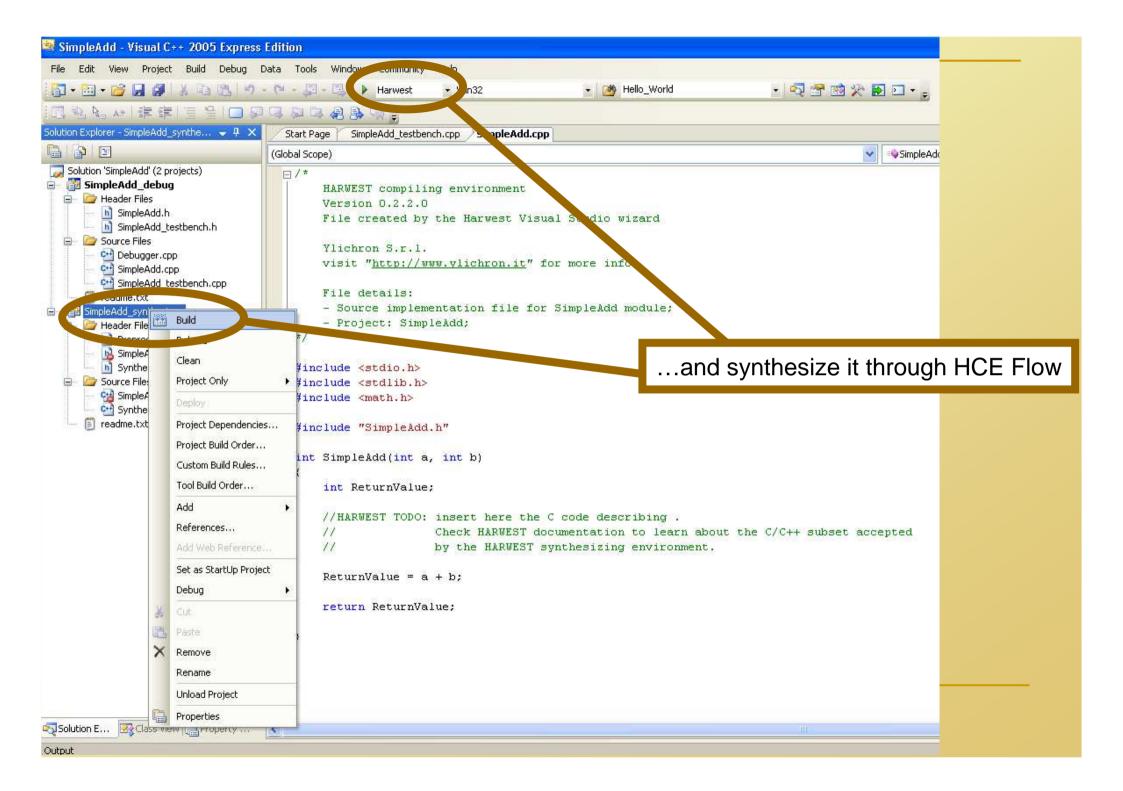

# Creating a new project ...

| 😫 Start Page - Visual C++ 2005 Express Edition                           |                  |                                         |  |  |  |  |  |

|--------------------------------------------------------------------------|------------------|-----------------------------------------|--|--|--|--|--|

| File Edit View Tools Window Community Help                               |                  |                                         |  |  |  |  |  |

|                                                                          | -                | 🕞 🌁 Hello_World 🛛 🔹 🗖 🖄 🏷 🛃 🖸 👻 👳       |  |  |  |  |  |

| Solution Explorer + 4 × Start Page                                       |                  |                                         |  |  |  |  |  |

| Microsoft<br>Visual C++ 2005<br>Express Edition                          |                  |                                         |  |  |  |  |  |

| Recent Projects                                                          |                  | eusl C1 / Douslanes Nowe                |  |  |  |  |  |

| MTranspose_2                                                             | New Project      | 28                                      |  |  |  |  |  |

| MTranspose_1                                                             | Project types:   | Templates:                              |  |  |  |  |  |

| SGEMM_Sc_Fixed                                                           | 🖃 Visual C++     | Visual Studio installed templates       |  |  |  |  |  |

| Hello_sc_World                                                           | CLR<br>Win32     | Harwest project                         |  |  |  |  |  |

| Hello_World                                                              | General          | My Templates                            |  |  |  |  |  |

| Open: Project<br>Create: Project                                         | hwst             | Search Online Templates                 |  |  |  |  |  |

| Getting Start<br>Ut Let + Express General Int<br>Do create an HARWEST Pr | oject            |                                         |  |  |  |  |  |

|                                                                          | Create a new Har | Create a new Harwest project            |  |  |  |  |  |

|                                                                          | Name:            | SimpleAdd                               |  |  |  |  |  |

|                                                                          | Location:        | C:\HARWEST\examples\Prova               |  |  |  |  |  |

| Visual C++ Express Headlin                                               | Solution Name:   | SimpleAdd Create directory for solution |  |  |  |  |  |

| Aiutateci a migliorare Visua<br>2005 inviandoci commenti e               |                  | OK Cancel                               |  |  |  |  |  |

| Output                                                                   |                  |                                         |  |  |  |  |  |

| YLICHRON                                                                 |                  |                                         |  |  |  |  |  |

| echnologies for Computing Systems Design                                 |                  |                                         |  |  |  |  |  |

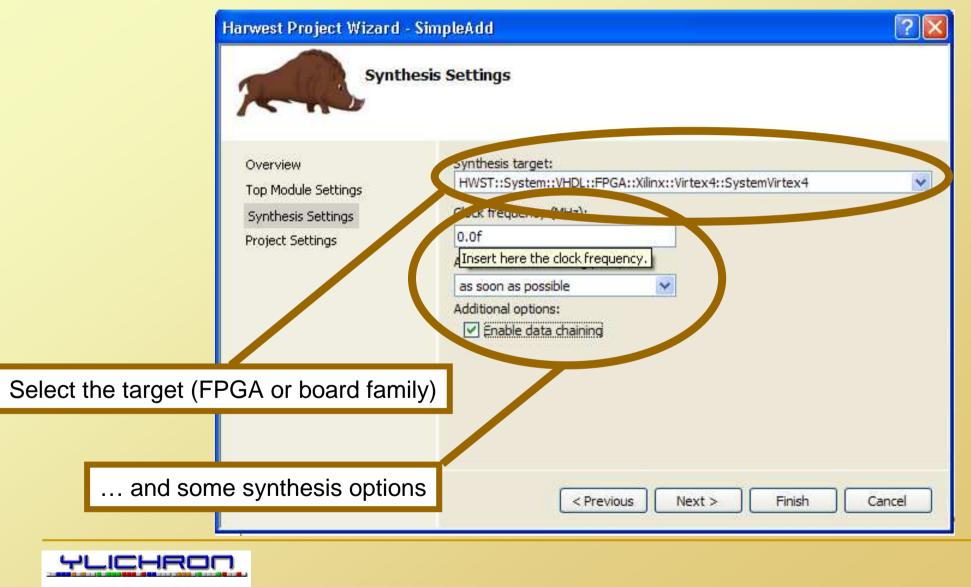

# ... and configuring it

# ... and configuring it

# ... and configuring it

| Proje                                                                     | ct Settings                                                                                                 | I do not need SystemC supp |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------|

| Overview<br>Top Module Settings<br>Synthesis Settings<br>Project Settings | Project settings<br>Use SystemC Data<br>Create debug pro<br>Generate graphic<br>Verbosity level:<br>level 0 | roject                     |

# HCE Output Files

| File Modifica Visualizza Preferiti Strumenti ?                                                                                                                                                                                                         |                 |                                                                                       |            |                                                          |                                                                                                  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------|------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| Indirizzo C:\HARWEST\examples\Prova\SimpleAdd\Sim<br>Cartelle                                                                                                                                                                                          | bleAdd\VHDL\SRC | Nome 🔺                                                                                | Dimensione | Тіро                                                     | Data ultima modifica                                                                             |  |  |  |

| <ul> <li>□ □ SimpleAdd</li> <li>□ □ debug</li> <li>□ □ SimpleAdd</li> <li>□ □ C_SRC</li> <li>□ □ CDFG</li> <li>□ Debug</li> <li>□ □ FSM</li> <li>□ □ FSM</li> <li>□ □ System</li> <li>□ □ VHDL</li> <li>□ SIM</li> <li>□ SIM</li> <li>□ SIM</li> </ul> |                 | AddModule_int_int_int<br>OutputModule_int<br>SimpleAdd_Ctrlpath<br>SimpleAdd_Datapath | 4 KB       | File VHD<br>File VHD<br>File VHD<br>File VHD<br>File VHD | 02/05/2008 11.41<br>02/05/2008 11.41<br>02/05/2008 11.41<br>02/05/2008 11.41<br>02/05/2008 11.41 |  |  |  |

# The CDFG

# Outline of presentation

- Why using the ANSI C

- What is HCE

- How HCE works

- Example of HCE use

- The DRC co-processing boards

- HCE performances

- Conclusions

# DRC co-processing boards

- DRC provides a co-processor system which fits on a free Opteron socket.

- Due to the tight interconnection to the host buses it provides high communication bandwidth between the host and the co-processor system.

- At the moment of writing the system is provided in two versions: RPU110-L60 and DRC RPU110-L200, both based on the Xilinx Virtex4 FPGAs (LX60 and LX200)

DRC co-processing boards

DRC co-processor system is equipped with:one Xilinx Virtex4 FPGA

HyperTransport (HT) interconnection;

Up to 2GB of RPU DRAM with two independent physical buses each with 3.2GB/s peak bandwidth;

DRC co-processing boards

128 MB of RPU Low Latency RAM (LLRAM) with two independent physical buses each with 800Mb/s peak bandwidth;

256 Mbits of not volatile Flash RAM

# Outline of presentation

- Why using the ANSI C

- What is HCE

- How HCE works

- Example of HCE use

- The DRC co-processing boards

- HCE performances

- Conclusions

### Performances

- test 1: measure of Read/Write bandwidth

- test 2: measure of internal memory bandwidth

- test 3: Boolean computation (graph transitive closure)

- test 4: DNA sequences (Smith Watermann)

- test 5: fixed point computations (FIR filter)

- test 6: floating point computations (Cannon algorithm for the matrix product)

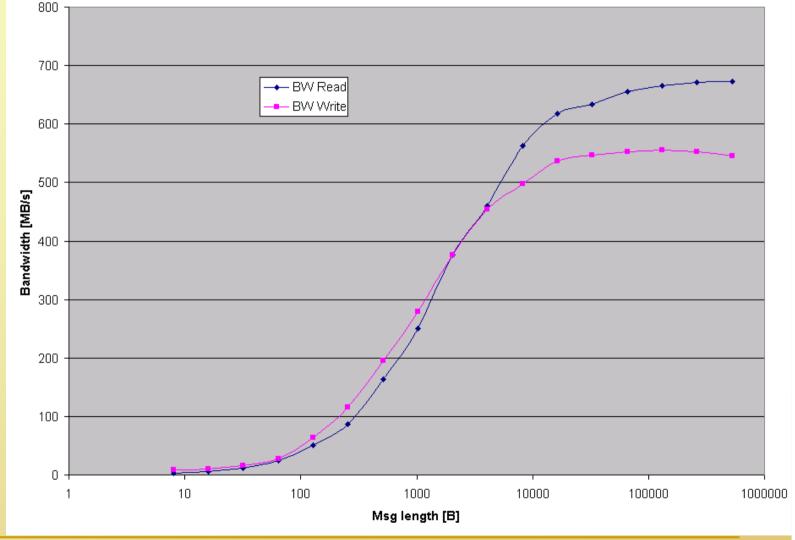

## test 1: measure of Read/Write bandwidth

Write: host  $\Rightarrow$  DRC Read: DRC  $\Rightarrow$  host

The time necessary to write (read) the shortest message (8 bytes) is equal to 0.9 µs (2.5 µs ).

#### test 2: measure of internal memory bandwidth

- The test performs the transposition of a 2D square matrix, copying the original matrix m[M][M] into the transposed matrix mT[M][M], (M=128)

- 136 clock cycles to transpose the matrix.

- f<sub>ck</sub>=100 MHz,

- MxMx4 bytes are read and written in 1.36 μs

- BW<sub>Read</sub>=BW<sub>Write</sub>=45 GB/s.

- slices used: 6601 (7% of the total for a Virtex4 LX200 FPGA).

- Block RAM modules used: 256.

### test 3: graph transitive closure

- G(N) graph represented through its boolean incidence matrix a[N][N] (N = 2048)

- T<sub>EXE</sub> = 250 ms, corresponding to 2\*N\*N/T<sub>EXE</sub> = 68 x 10<sup>9</sup> op/s.

- slices used: 3695 (4% of the total for V4LX200)

- Block RAM modules used: 256

### test 4: Smith Watermann

- SW uses a dynamic programming approach to find the best alignment (with insertions, deletions and mismatches) between a DNA sequence of size m (=255) and another sequence of size n (1024).

- Implemented the computation of the scoring matrix

- HCE run time: 53 µs, corresponding to 5 GScoreUpdate/sec

- fck = 100 MHz.

- slices used: 20897 (23% of the total for V4LX200).

### test 5: FIR filter

- Filter: 128 taps

- Input signal x[N] (N = 1024)

- Both the filter taps and the samples used the sc\_fixed<16,8> SystemC data type

- f<sub>ck</sub> = 60 MHz, T<sub>EXE</sub>=17 μs

- sustained computation rate of 14 Gop/s,

- slices used: 30489 (34% of the total for V4LX200)

- all the 96 available DSP blocks have been used

# test 6: GEMM Cannon algorithm

- Parallel formulation of the MM algorithm, often used for systolic implementation

- MatSize M = 128

- f<sub>ck</sub> = 80 MHz, T<sub>EXE</sub> = 3.7 ms

- sustained computation rate of 1.1 GFlop/s,

- slices used: 40799 (45 % of the total for V4LX200)

- all the 96 available DSP blocks have been used

- Block RAM modules used: 98

# Outline of presentation

- Why using the ANSI C

- What is HCE

- How HCE works

- Example of HCE use

- The DRC co-processing boards

- HCE performances

- Conclusions

## Conclusions

- The HCE, a C to VHDL automatic design suite has been presented;

- Its theoretical bases have been revised;

- Its use (and usability) has been discussed;

- Some performance figure have been reported;

Contact information

Commercial: info@ylichron.it

Technical: <u>support@ylichron.it</u>

Web site: <u>http://www.ylichron.it</u>