## Changing Needs/Solutions/Roles

Rajeeb Hazra

Vice President, Data Center Group

General Manager, Enterprise & High Performance Computing Platforms

Intel Corporation

### **Three Decades of High Performance Computing**

#### **Vertically integrated**

Cray - 1 (1975) 250 MFLOPS

- Fewer fast proprietary processors

- Custom software

- ~\$5-8M System Cost

- Government labs

#### **Massively Parallel**

Connection Machine - 2 (1987)

2.5 GFLOPS

- Unix, VMS and proprietary programming models

- □ ~\$5M System Cost

- Scientific & Commercial

#### **Democratized HPC**

Beowulf Cluster (1996) 1+ GFLOPS

- Commodity compute, network, & storage

- ☐ Standard Linux & parallel programming models

- □ ~\$50K System cost

- ☐ Government Labs, Academia & Commercial

#### Intel's Role: The x86 "Ecosystem"

The Past: '00-'05

The Present: '06-Today

Ad Hoc: Few, incompatible HPC system vendors

Intel: supply silicon

ICR Platform Spec: ecosystem of many compatible system & apps

Intel: enable interoperability

*Is the Future More of the Present?*

## The Writing On The Wall

#### **Technology Disruptions**

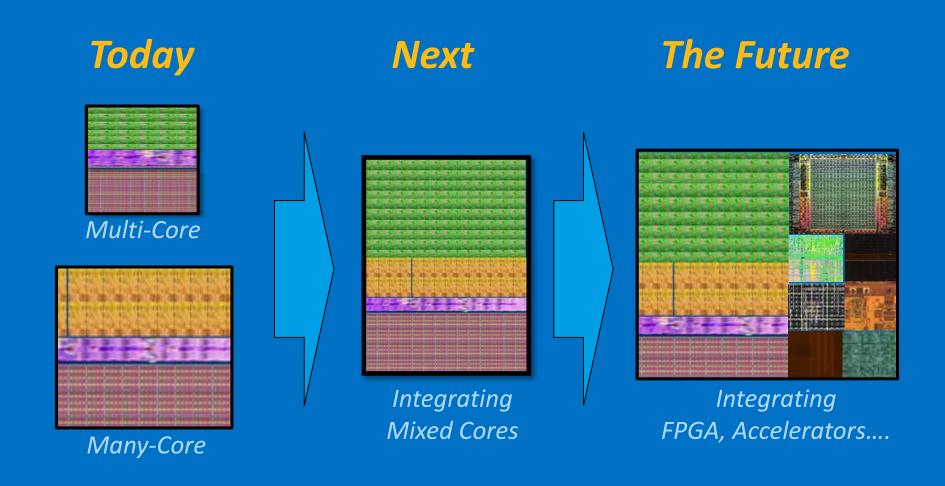

Integration

Storage Re-architecture

**Software Transformation**

#### **Increased Demand**

New users & usages ... Cloud makes HPC more accessible

Real-time analytics using HPC

**ARM**<sup>®</sup> Indigenous CPU interests

#### **Channel Challenges**

*Increasing complexity* **Software Fragmentation** Differentiation New market makers

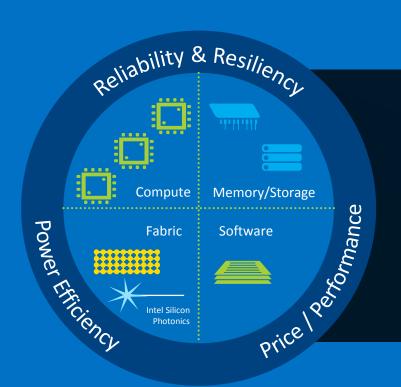

## Intel's HPC Scalable System Framework (SSF)

A design foundation enabling wide range of highly workload-optimized solutions

Small clusters to Supercomputers

Compute and Data-Centric Computing

Standards-Based Programmability

Intel® Xeon® Processors

Intel® Xeon Phi<sup>™</sup> Coprocessors

In Package Memory

Intel® True Scale Fabric Intel® Omni-Path Fabric Intel® Ethernet Intel® Silicon Photonics Technology Next-generation NVM

Intel® SSDs

Intel® Lustre\*-based Solutions

Intel® Sofware Tools

Intel Cluster Software

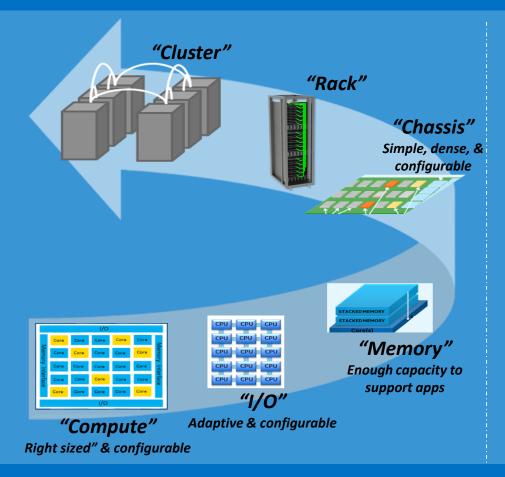

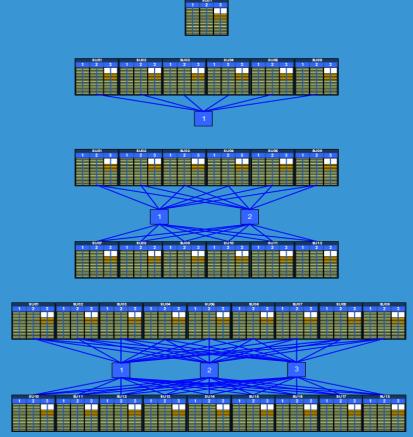

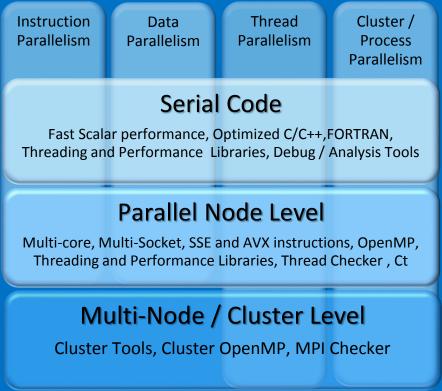

#### SSF: Enabling Configurability & Scalability

from components to racks to clusters

- Intel Xeon or Xeon Phi processors based on workloads

- Compute flexibly aggregated

- Low latency compute to compute interconnect

- I/O Topologies for high performance

- Configurable I/O bandwidth director switch

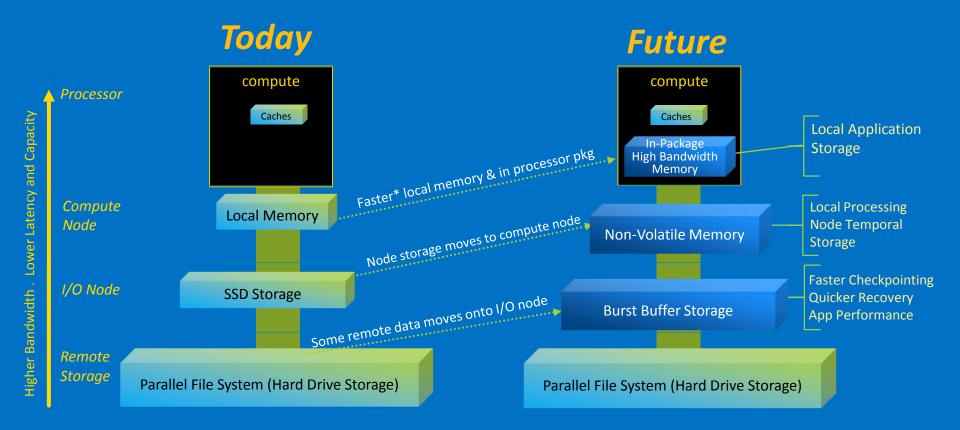

- Burst buffer to decouple storage from I/O

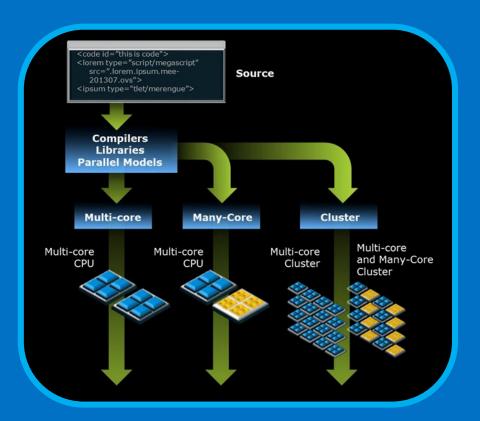

## SSF: Accommodating New Compute Paradigms

# SSF: Re-architecting The Memory-Storage Hierarchy

Better data-intensive app performance and energy efficiency

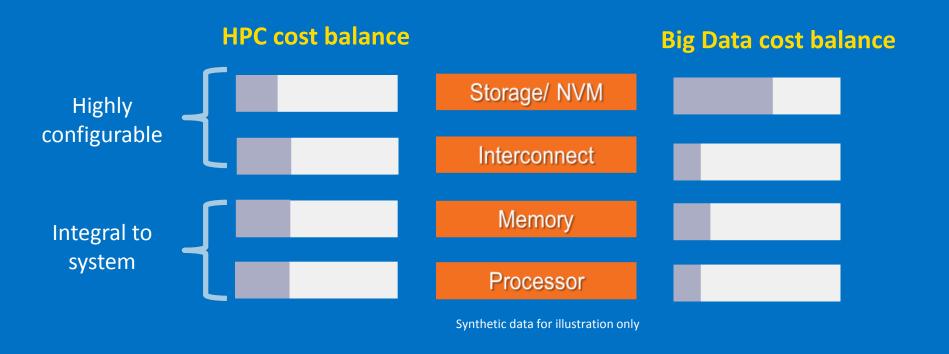

#### SSF: End The "Big Data vs. HPC" Debate

A single, broadly configurable, framework to meet both requirements from a hardware perspective

#### SSF: Enabling A Single Programming Model

Unlike accelerators, optimizations for Intel® Xeon Phi™ and Intel® Xeon® products share the same languages, directives, libraries, and tools

#### **Modernizing Community Codes**

Together With You

Intel Parallel

Computing

Centers

50+ Centers 14 countries 80+ codes

## **Heading To The Era of SSF**

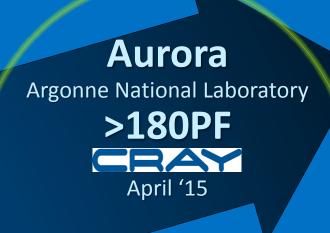

ANL selected Intel and Cray for Extreme Scale HPC

Cori

NERSC‡

>30PF

April '14

Trinity

NNSA†

>40PF

July'14

Theta

Argonne National Laboratory

>8.5PF

>\$200M

<sup>‡</sup> Cray XC Series at National Energy Research Scientific Computing Center (NERSC).

<sup>†</sup> Cray XC Series at National Nuclear Security Administration (NNSA). \*Other names and brands may be claimed as the property of others.

Look Inside.™

## Legal Notices and Disclaimers

- Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

- No computer system can be absolutely secure.

- Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

- Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

- This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

- Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit <a href="https://www.intel.com/performance">https://www.intel.com/performance</a>.

- Optimization Notice: Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for

optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction

sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on

microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with

Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors.

Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets

covered by this notice. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted

by this document.

- Intel, the Intel logo, Xeon, Xeon Phi and others are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others.

- © 2015 Intel Corporation.